近日,英特尔对外分享了英特尔封装技术路线图。英特尔院士、封装研究与系统解决方案总监Johanna Swan分享道,从标准封装到嵌入式桥接时,凸点间距从 100 微米变为 55-36 微米。到Foveros封装时,英特尔将芯片堆叠在一起,实现横向和纵向的互连,凸点间距大概是50微米。未来,英特尔将通过采用Hybrid Bonding(有两种翻译:混合键合、混合结合)技术,计划实现小于 10 微米的凸点间距。

将凸点间距缩小到小于10微米, Hybrid Bonding技术究竟是如何实现的?

英特尔今年曾在ECTC 上发表关于混合键合技术的论文。Johanna Swan介绍,混合键合技术是一种在相互堆叠的芯片之间获得更密集互连的方法,并帮助实现更小的外形尺寸。

当缩减到大约 10 微米的凸点间距,将能够达到每平方毫米 10,000 个凸点。 这样,两个芯片之间能够实现更多的互连,进而可以提供更小、更简单的电路,因为它们可以相互叠加,也不必做扇入(fan-in)和扇出(fan-out)。

“有了这个更简单的电路,我们可以使用更低的电容, 然后开始降低该通道的功率,这有助于朝着提供最好产品方向发展。” Johanna Swan表示。

Hybrid Bonding与Foveros 技术所实现的焊接有诸多区别。

混合键合技术使电介质的芯片非常光滑,而不是有一个突出的凸点。实际上,还会有一个略微的凹陷。 当采用混合键合技术将两个组件放在一起时,可以在室温下进行,将它们放置好后,再升高温度对其进行退火,铜在这时会膨胀,从而形成电气连接。

Johanna Swan认为:“这非常有用,因为可获得更高的载流能力,并且可以将间距缩小到 10 微米以下。这样使我们目前在这些接口之间获得了比底部填充和紧密的铜密度更好的热性能。当使用混合键合技术时,将需要一种新的制造、清洁和测试方法。”

转向更小的间距可能会更有吸引力。 英特尔正在转向多个晶片,将其分解成 GPU、CPU、IO或区块,之后或许可以使用更小的区块去拥有单独的 IP, 这使得拥有更多区块,进而可以重复使用。Johanna Swan指出,这项技术可以根据特定客户的独特需求定制产品。 这种技术可改变晶片到晶片的互连,从焊接转向混合键合。

如果必须保持制造流程以相同的速度进行,当又有更多的晶片需要放置时,需要如何应对?为此,英特尔正在考虑的解决方案是批量组装,简称“自组装”。

当前,英特尔正在与 CEA-LETI(法国原子能委员会电子与信息技术实验室) 合作,研究一次能够放置多个晶片,并且进行自组装。

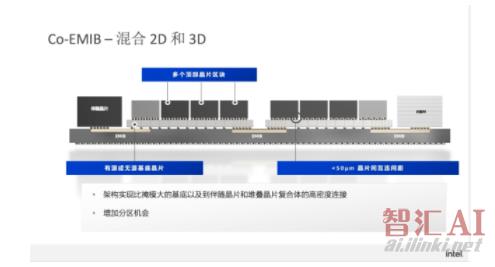

在可扩展性轴上,包括CO-EMIB技术和ODI 全方位互连技术。

CO-EMIB技术尝试通过使用 EMIB 和 Foveros 的组合来融合 2D 和 3D 的技术, 这种架构基于与配套晶片和堆叠芯片复合体的高密度连接,实现了比基础尺寸更大的尺寸。

ODI 全方位互连技术,是英特尔正在使用的封装的一个新维度。

对于2.5D 和 3D的组合,Johanna Swan指出,这种趋势肯定会继续下去,因为拥有的发展机会是在每毫米立方体上提供尽可能多的区块并获得每毫米立方体尽可能多的功能。封装将继续小型化和缩小尺寸,以便可以获得毫米立方体的最大功能。

英特尔的 Foveros技术,通过该技术堆叠芯片,使用硅通孔Through -Silicon-Via(TSV) 技术在封装和晶片之间通信,一直到顶部晶片。

然而,ODI 封装技术是另一种优化,通过添加 ODI 封装技术为客户进行定制。在右侧添加了支柱,允许最右侧的顶部管芯直接连接到封装,这使得可以将较小的 TSV 芯片面积用于硅通孔 (TSV),进而减少数量。这些支柱提供了直接向顶部晶片封装供电的能力。顶部的两个晶对下部的晶片有更高的带宽、更小的凸点、更小的通道。

对于如何推动封装的不断演进,Johanna Swan认为:“封装是一个差异化优势的区分因素,关键是客户。我们努力服务并提供独特的解决方案给客户,这也推动了我们关注技术。因此,封装的机会在于,随着继续为客户提供服务,客户的产品需求在不断进化,这才是真正推动封装技术需要转变的原因。客户的这种差异化需求也会推动相应的封装技术的出现。

为了满足客户的需求,晶圆制造企业开始致力于先进封装技术,这也将晶圆制造与封装两个环节的界线开始模糊。对于两者今后的发展趋势,Johanna Swan也表达了自己的理解:“在 10 微米间距的混合键合时,这两个世界已经开始融合,我开始研究我们正在使用的金属层的特征低于 10 微米,像 4 微米。晶圆制造和封装正在融合,这已经成为一个非常重要、有趣的创新场所,因为它们的尺寸相同,所以这种放置是非常令人兴奋的,使用具有封装测试技术的传统晶圆厂工具并创造出我们在封装方面进行创新的全新领域。

(审核编辑: 智汇小新)